# **DESIGN AND ANALYSIS OF CARRY** MASKABLE ADDER (CMA) FOR LOW POWER APPLICATION

<sup>1</sup>Mr.P.Raghava Reddy, <sup>2</sup>O.Venkateswarlu, <sup>3</sup>M.RamCharan Reddy, <sup>4</sup>N.Sudheer, <sup>5</sup>K.Mohith Babu <sup>1</sup>Assoc.Professor, <sup>2,3,4,5</sup>B.Tech students <sup>1,2,3,4,5</sup> Department of Electronics and Communication Engineering 1,2,3,4,5 Geethanjali Institute of Science and Technology, Nellore, India.

# Abstract:

Expansion is a key essential capacity for some error tolerant applications. Estimated expansion is viewed as a productive system for exchanging off vitality against execution and exactness. This paper proposes a carry maskable snake whose exactness can be designed at runtime. The proposed plan can progressively choose the length of the convey spread to fulfil the quality prerequisites adapt- ably. Contrasted and an ordinary swell convey viper and a traditional convey look-ahead snake, the proposed 16-bit snake decreased power utilization by 54.1% and 57.5% and basic way delay by 72.5% and 54.2%, individually. Also, results from a picture handling application show that the nature of the prepared pictures can be constrained by the proposed viper.

# I.INTRODUCTION

Numerous inexorably famous applications, for example, picture handling and acknowledgment, which are computationally requesting, have made provokes with respect to control utilization. A large portion of these applications are innately tolerant of little errors; therefore, there are remarkable chances to diminish control utilization. Expansion is a crucial number juggling capacity for such applications. Rough processing is an effective methodology for blunder tolerant applications since it can exchange off precision for power. As of now, this tradeoff assumes a critical job in such application areas. Since the quality prerequisites of an application may shift altogether at runtime, it is desirable over structure quality-configurable frameworks that can exchange off calculation quality as indicated by application necessities. In this paper, we center around the structure of an accuracy configurable viper plan from the part of intensity utilization. Our essential commitment is to accomplish precision configurability productively by marginally adjusting a traditional snake with the goal that a portion of its rationale entryways can be reused. We propose a viper in which the age circuit of each piece of its whole can be powerfully arranged to work as a full snake or an OR entryway. This configurability is acknowledged by covering convey engendering. We executed the proposed viper, a regular swell convey snake (RCA), and a customary convey look-ahead viper (CLA) in Verilog HDL utilizing a 45-nm library and assessed their capacity utilization, basic way deferrals, and plan regions. Convey in Prediction Adder Unit MUX C0 A0 B0 Control 0 S0 Carry-in Prediction Adder Unit MUX C1 A1 B1 Control 1 S1 Carry-in Prediction Adder Unit MUX C2 A2 B2 Control 2 S2 Adder Unit C3 A3 B3 S3 Figure 1: Accuracy effortlessly debasing viper in [5]. Examinations with the ordinary RCA and CLA demonstrate that, with a 1.95% mean relative mistake separate (MRED), the proposed viper decreases control utilization by 54.1% and 57.5%, individually. We give a transversely correlation with show the prevalence of the proposed viper looked at over the current methodology. We executed one of the set up exactness configurable adders to assess control utilization, structure zone, basic way postponement, and precision. We likewise assessed the nature of these two accuracy configurable adders in a genuine picture preparing application.

# II. LITERATURE SURVEY

Gupta examined how to disentangle the multifaceted nature of an ordinary mirror viper cell at the transistor level. Mahdiani proposed a lower-part-OR snake, which uses OR entryways for the expansion of the lower bits and exact adders for expansion of the upper bits. Venkatesan proposed to develop an identical untimed circuit that speaks to the conduct of an estimated circuit. Miao presented an adjusted fixed inner convey structure and afterward proposed a vacillating surmised viper by exchanging off blunder extent and mistake recurrence. They portrayed a theoretical convey select snake with solid variable inactivity to identify mistakes and recoup results. Practically speaking, the calculation quality necessity of an application may differ essentially at runtime. The above static rough structures with fixed exactness may neglect to meet application quality prerequisite or waste power when high caliber isn't required. This implies surmised adders ought to be powerfully configurable to coordinate the distinctive quality prerequisites of various program stages. To adjust to changing precision prerequisites of various outstanding tasks at hand, Kahng proposed an accuracy configurable viper (ACA) in view of a pipeline structure. The redress plan of the ACA continues from stage 1 to stage 4. This implies, if the most huge bits of the outcomes are required to be right, the majority of the four phases ought to be performed.

Persuaded by the abovementioned, proposed a precision effortlessly debasing viper (GDA). As showed in Fig. 1, each sub snake hinder, with the exception of the furthest right one, has its own convey in forecast square, viper unit, and multiplexer. Do signs can be chosen from either the viper units or convey in forecast hinders by control motions in any request. Like viper proposed in this paper does not consider a pipeline structure. To produce yields with various dimensions of calculation precision and to acquire the configurability of exactness, a few multiplexers and extra rationale squares. The extra rationale squares cause region overhead and power squander when their yields are not used to produce an entirety. As appeared in the GDA in Fig. 1, if all S0, S1, S2, and S3 are required to be exact, the power utilization of the carry-in forecast rationale squares will be squandered. To handle this issue, just a convey veil flag was added to our proposed viper to accomplish precision configurability. To the best of our insight, this is the main examination that has accomplished an exactness configurable snake without multiplexers to choose inexact and precise wholes. In this way, no extra circuits, for example, convey in expectation or blunder recuperation rationale squares, are required.

Figure 1: Accuracy gracefully-degrading adder

#### III. EXISTING METHOD

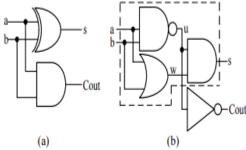

An ordinary half viper is appeared in Fig. 2(a). A 2-input XOR entryway is utilized to create aggregate s and a 2-info AND door is utilized to produce convey Cout. A proportionate circuit of a half snake is appeared in Fig. 2(b). The dashed casing speaks to an equal circuit of a 2-input XOR entryway. Since there is a 2-input NAND entryway in the dashed casing, we reuse it and add an INV door to produce the convey flag Cout. The yields of the 2-input NAND or potentially entryways in the dashed edge are named u and w, individually. Table 1 is reality table for the proportionate circuit of a half snake. As appeared in Fig. 2(b) and Table 1, when the inside flag u is 1, the entirety s is equivalent to an OR b and the convey Cout is 0. This implies, if u is controllable and can be controlled to 1, the convey proliferation will be conceal and the whole s will be equivalent to an OR b. The aggregate s = an OR b is not quite the same as the precise whole (=a XOR b) just when both an and b are 1. At the end of the day, the whole s = an OR b can be considered as a surmised total. The selectivity between the exact and surmised entireties can be accomplished by a control flag, which is utilized to control u to be a NAND b, or to be 1.

Figure 2: (a) Conventional half adder, and (b) equivalent circuit of a half adder.

Table 1: Truth table for the equivalent circuit of a half adder.

| Inputs |   | Internal signals |   |   |      |  |

|--------|---|------------------|---|---|------|--|

| a      | b | u                | w | S | Cout |  |

| 0      | 0 | 1                | 0 | 0 | 0    |  |

| 0      | 1 | 1                | 1 | 1 | 0    |  |

| 1      | 0 | 1                | 1 | 1 | 0    |  |

| 1      | 1 | 0                | 1 | 0 | 1    |  |

#### IV. Proposed method

#### a. Carry-Maskable Adder

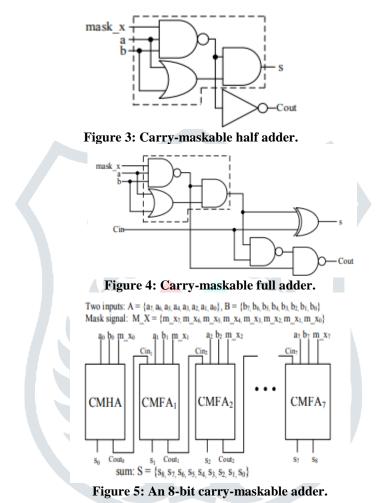

In this system, we include a flag named "mask\_x" as the control flag and utilize a 3-input NAND entryway to supplant the 2-input one in the dashed casing in the ordinary half viper. This is known as a convey maskable half snake (CMHA) and appeared in Fig. 3. At the point when  $mask_x = 0$ , the aggregate s = an OR b, and the convey Cout = 0; generally, when  $mask_x = 0$ 1, the total s = a XOR b, and the convey Cout = an AND b. Comparative contemplations apply to a full snake, which is appeared in Fig. 4. At the point when  $mask_x = 0$  and Cin = 0, the aggregate s = an OR b, and the convey Cout = 0, at that point clearly exchanging exercises become littler, and dynamic power utilization is diminished. This full snake is known as a convey maskable full viper (CMFA). A n-bit viper, which is actualized utilizing one CMHA and (n-1) CMFA, is called a n-bit convey maskable snake (CMA).

Fig. 5 shows an 8-bit CMA as an example. The convey cover flag M\_X includes eight bits, which are indicated as m\_x0, m\_x1, ..., m x7. The left is the least critical piece in Fig. 5. The total and convey of the CMHA are s0 and Cout0, separately. Cin1 is associated with Cout0. At the point when m\_x0 is equivalent to 0, s0 = a0 OR b0, and Cin1 = Cout0 = 0. At the point when both m\_x1 and m\_x0 are equivalent to 0, s0 = a0 OR b0, Cin1 = Cout0 = 0, s1 = a1 OR b1, and Cout1 = 0 (Cin2 is likewise 0). At the end of the day, convey engendering from CMHA to CMFA1 is conceal. By extending the above conditions to CMFA7, when all  $m_x0$ ,  $m_x1$ , ...,  $m_x7$  are 0, all Cout0, Cout1, ..., Cout7 are 0, and s0 = a0 OR b0, s1 = a1 OR b1, ..., s7 = a7 OR b7, s8 = 0(s8 = Cout7). In this manner, the convey proliferation from CMHA to CMFA7 is conceal. Note that there are two conditions for veiling the convey proliferation of a CMFA: both m\_x and Cin's being 0. Considering the over 8-bit CMA, on the off chance that we need to veil the convey engendering from CMHA to CMFA3, we should set m\_x0, m\_x1, m\_x2, and m\_x3 to 0 (not set just m\_x3 to 0) to guarantee that Cin1, Cin2, and Cin3are equivalent to 0. Each CMFA, just as the CMHA has its very own convey cover motion in a CMA. Considering a 16-bit CMA, a 16-bit M X flag (m x0, m x1, ..., m x15) is required. To streamline the structure of a CMA, we can likewise aggregate some CMFAs as a sub snake unit. Fig. 6 is a 16-bit CMA with four sub snake units. Each sub viper unit has four CMFAs (aside from sub snake unit 0: one CMHA and three CMFAs) and 1-bit convey veil flag to cover convey spread. There is no convey cover motion for sub snake unit 3 in this precedent. The structure of sub snake unit 1 is appeared in Fig. 7 for instance. C0 is the yield of sub snake unit 0 and 1-bit mask\_x1 is the convey cover motion for sub viper unit 1. On the off chance that  $mask_x = 0$  and C0 = 0, we can acquire C1 = 0 and S1 = A1 OR B1 (4-bit parallel OR capacity). Note that the bit-length of each sub viper unit can be extraordinary.

# V. Results

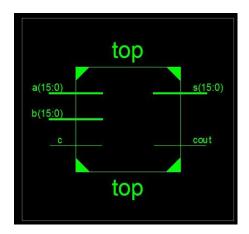

Fig 6: RTL Schematic

| Device Utilization Summary                    |      |           |             |         |  |

|-----------------------------------------------|------|-----------|-------------|---------|--|

| Logic Utilization                             | Used | Available | Utilization | Note(s) |  |

| Number of 4 input LUTs                        | 41   | 9,312     | 1%          |         |  |

| Number of occupied Slices                     | 26   | 4,656     | 1%          |         |  |

| Number of Sices containing only related logic | 26   | 26        | 100%        |         |  |

| Number of Slices containing unrelated logic   | 0    | 26        | 0%          |         |  |

| Total Number of 4 input LUTs                  | 41   | 9,312     | 1%          |         |  |

| Number of bonded <u>IOBs</u>                  | 50   | 232       | 21%         |         |  |

| Average Fanout of Non-Clock Nets              | 2.15 |           |             |         |  |

Fig 7: Design summary

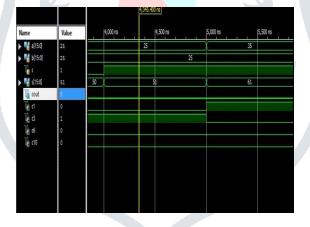

Fig 8: Simulation Results

# **VI.CONCLUSION:**

This paper proposes an exactness configurable rough viper that does not require any extra rationale squares to accomplish precision design. The exploratory outcomes exhibit that the proposed viper can convey more huge vitality investment funds than the traditional RCA and CLA while keeping up an altogether little circuit region. Contrasted with other recently examined adders, the test results from both the circuit and application levels show that our proposed viper conveys more prominent upgrades in vitality sparing, structure zone, and exactness.

#### **VII.REFERENCES**

- [1] S. Cotofana, C. Lageweg, and S. Vassiliadis, "Addition related arithmetic operations via controlled transport of charge", IEEE Transactions on Computers, vol. 54, no. 3, pp. 243-256, Mar. 2005.

- [2] V. Beiu, S. Aunet, J. Nyathi, R. R. Rydberg, and W. Ibrahim, "Serial Addition: Locally Connected Architectures", IEEE Transactions on Circuits and Systems-I: Regular papers, vol. 54, no. 11, pp. 2564-2579, Nov. 2007.

- [3] S. Venkataramani, V. K. Chippa, S. T. Chakradhar, K. Roy, and A. Raghunathan, "Quality programmable vector processors for approximate computing", 46th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO), pp. 1-12, Dec. 2013.

- [4] A. B. Kahng, and S. Kang, "Accuracy-configurable adder for approximate arithmetic designs", IEEE/ACM Design Automation Conference (DAC), pp. 820-825, Jun. 2010.

- [5] R. Ye, T. Wang, F. Yuan, R. Kumar, and Q. Xu, "On Reconfiguration-Oriented Approximate Adder Design and Its Application", IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 48-54, Nov. 2013.

- [6] V. Gupta, D. Mohapatra, A. Raghunathan, and K. Roy, "Low-Power digital signal processing using approximate adders", IEEE Transactions on ComptuerAided Design of Integrated Circuits and Systems, vol. 32, no. 1, pp. 124-137, Jan. 2013.

- [7] H. R. Mahdiani, A. Ahmadi, S. M. Fakhraie, and C. Lucas, "Bio-Inspired imprecise computational blocks for efficient VLSI implementation of Soft-Computing applications", IEEE Transactions on Circuits and Systems I: Regular papers, vol. 57, no. 4, pp. 850-862, Apr. 2010.

- [8] R. Venkatesan, A. Agarwal, K. Roy, and A. Raghunathan, "MACACO: modeling and analysis of circuits for approximate computing", IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 667-673, Nov. 2011.

- [9] J. Miao, K. He, A. Gerstlauer, and M. Orshansky, "Modeling and Synthesis of Quality-Energy Optimal for Approximate Adder", IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 728-735, Nov. 2012.

- [10] K. Du, P. Varman, and K. Mohanram, "High performance reliable variable latency carry select addition", IEEE/ACM Design, Automation Test in Europe (DATE), pp. 1257-1262, Mar. 2012.

- [11] NanGate, Inc. NanGate FreePDK45 OpenCellLibrary, http://www.nangate.com/?page\_id=2325, 2008

- [12] J. Liang, J. Han, and F. Lombardi, "New metrics for the reliability of approximate and probabilistic adders", IEEE Transactions on computers, vol. 62, no. 9, pp. 1760-1771, Sep. 2013.

- [13] M. S. Lau, K. V. Ling, and Y. C. Chu, "Energy-Aware probabilistic multiplier: Design and Analysis", International Conference on Compliers, architecture, and synthesis for embedded systems, pp. 281-290, Oct. 2009.